PCIe 中断机制介绍(MSI-X)

2024-06-27

65

0

PCI总线自3.0版本开始支持MSI-X机制,对MSI做出了一些升级和改进,以克服MSI机制的三个主要的缺陷:

- 随着系统的发展,对于特定的大型应用,32个中断向量不够用了(参考前一篇文章);

- 只有一个目标地址使得多核CPU情况下的,静态中断分配变得困难。如果能够使每个向量对应不同的唯一的地址,便会灵活很多;

- 某些应用中的中断优先级混乱问题。

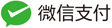

有趣的是,MSI只支持32个中断向量,而MSI-X支持多达2048个中断向量,但是MSI-X的相关寄存器在配置空间中占用的空间却更小。这是因为中断向量信息并不直接存储在这里,而是在一款特殊的Memory(MIMO)中。并通过BIR(Base address Indicator Register, or BAR Index Register)来确定其在MIMO中的具体位置。如下图所示:

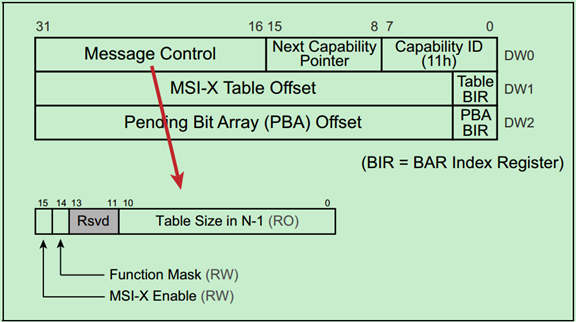

Message Control寄存器的具体描述如下:

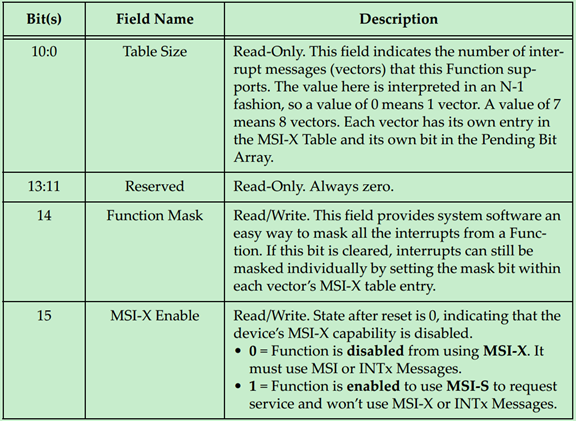

MSI-X查找表的示意图如下:

结构图如下:

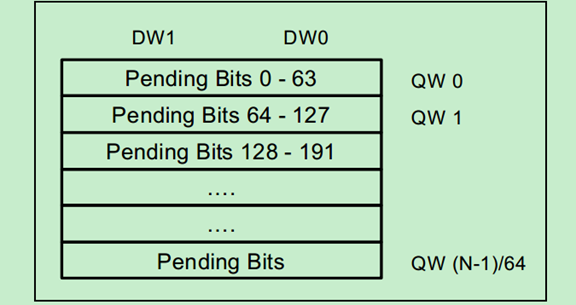

类似的,Pending Bits则位于另一个Memory中,其结构图如下:

注:无论是MSI还是MSI-X,其本质上都是基于Memory Write 的,因此也可能会产生错误。比如PCIe中的ECRC错误等。

原文转自:http://blog.chinaaet.com/justlxy/p/5100057843

PCIe扫盲系列(四)

PCIe扫盲系列(四)