PCI总线66MHz的技术瓶颈

2024-06-26

18

0

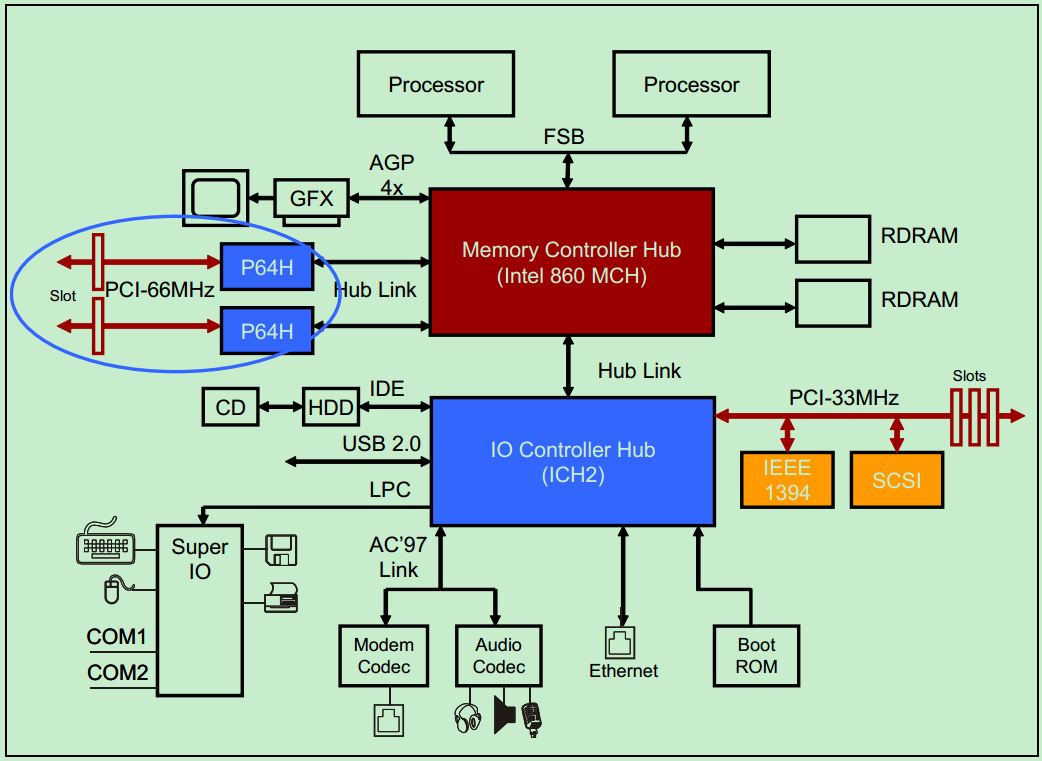

为了能够取得更高的带宽,新版本的PCI Spec将PCI总线提高到了64-bit并将频率提高到了66MHz,最高支持533MB/s。下图描述的是一个典型的66Mhz,64-bit的PCI系统结构图。

前面的文章介绍过,PCI总线采用了Reflected-Wave Signaling技术,因此总线频率的提高,必然会导致总线负载能力的降低。结果就是,66MHz 64-bit的PCI总线只能支持一个PCI插卡设备(算作两个PCI设备,插槽和PCI卡各算一个)。为了增加整个系统的PCI设备数,就不得不去增加额外的PCI桥,这又进一步增加了功耗,提高了成本。此外,64-bit的PCI总线由于增加了很多的引脚,导致66MHz 64-bit的PCI总线的稳定性降低,对PCB的设计提出了更高的要求,也限制了其广泛应用。

此外,由于PCI总线采用的是non-registered输入,这要求输入信号的建立时间至少要有3ns,而66MHz的时钟下,周期为15ns,剩余的12ns基本上都被Reflected-Wave Signaling给消耗了。因此,66MHz基本上算是PCI总线的频率的上限了。

在PCI-X总线中,为了解决上诉问题,PCI-X总线将所有的输入信号都先用寄存器打一拍,此时对输入信号的建立时间的要求就不在那么苛刻了,因此PIC-X总线可以运行在更高的频率上(100MHz,甚至133MHz)。

原文转自:https://blog.chinaaet.com/justlxy/p/5100053221

PCI基础

PCI基础