串口发送数据

2024-04-30

57

0

always@(posedge clk or posedge reset)

if(reset)

bps_DR <= 16'd5207;

else begin

case(baud_set)

0:bps_DR <= 16'd5207;

1:bps_DR <= 16'd2603;

2:bps_DR <= 16'd1301;

3:bps_DR <= 16'd867;

4:bps_DR <= 16'd433;

default:bps_DR <= 16'd5207;

endcase

end

//波特率计数器

always@(posedge clk or posedge reset)

if(reset)

div_cnt <= 16'd0;

else if(uart_state)

begin

if(div_cnt == bps_DR)

div_cnt <= 16'd0;

else

div_cnt <= div_cnt + 1'b1;

end

else

div_cnt <= 16'd0;

end

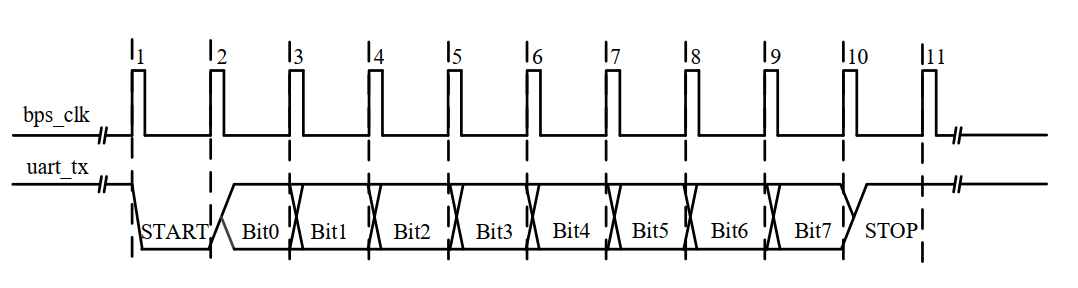

// 波特率计数到时,bps_clk触发一个上升沿,用于通知进行下一位

always@(posedge clk or posedge reset)

if(reset)

bps_clk <= 1'b0;

else if(div_cnt == 16'd1)

bps_clk <= 1'b1;

else

bps_clk <= 1'b0;

end

//由bps_clk上升沿触发,位移

always@(posedge clk or posedge reset)

if(reset)

bps_cnt <= 4'd0;

else if(bps_cnt == 4'd11)

bps_cnt <= 4'd0;

else if(bps_clk)

bps_cnt <= bps_cnt + 1'b1;

else

bps_cnt <= bps_cnt;

end

always@(posedge clk or posedge reset)

if(reset)

tx_done <= 1'b0;

else if(bps_cnt == 4'd11) //bps count计数到11时,表示发送完成

tx_done <= 1'b1;

else

tx_done <= 1'b0;

//uart_state=1时表示发送,否则为空闲

always@(posedge clk or posedge reset)

if(reset)

uart_state <= 1'b0;

else if(send_en)

uart_state <= 1'b1;

else if(bps_cnt == 4'd11)

uart_state <= 1'b0;

else

uart_state <= uart_state;

end

//数据设置

always@(posedge clk or posedge reset)

if(reset)

data_byte_reg <= 8'd0;

else if(send_en)

data_byte_reg <= data_byte;

else

data_byte_reg <= data_byte_reg;

end

//数据发送状态机

always@(posedge clk or posedge reset)

if(reset)

uart_tx <= 1'b1;

else begin

case(bps_cnt)

0:uart_tx <= 1'b1;

1:uart_tx <= START_BIT;

2:uart_tx <= data_byte_reg[0];

3:uart_tx <= data_byte_reg[1];

4:uart_tx <= data_byte_reg[2];

5:uart_tx <= data_byte_reg[3];

6:uart_tx <= data_byte_reg[4];

7:uart_tx <= data_byte_reg[5];

8:uart_tx <= data_byte_reg[6];

9:uart_tx <= data_byte_reg[7];

10:uart_tx <= STOP_BIT;

default:uart_tx <= 1'b1;

endcase

end

FPGA入门练习

FPGA入门练习