Verilog计数器练习

2024-04-30

56

0

计数器代码:

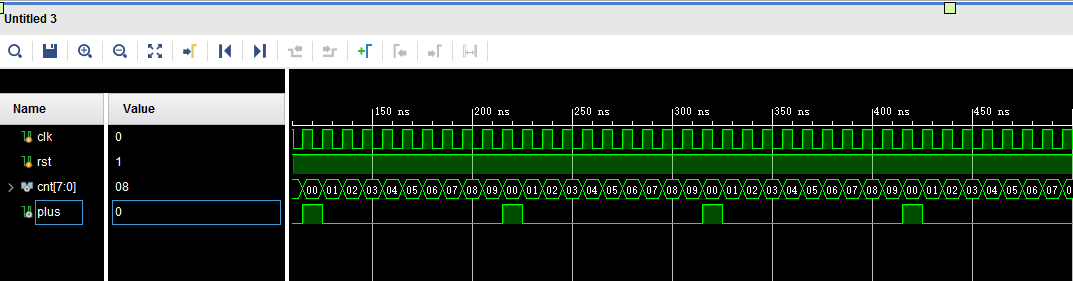

`timescale 1ns / 1ps

module cnt(input clk,input rst,output reg [7:0] cnt,output reg plus );

always@(posedge clk)

begin

if(!rst)

cnt <=0;

else if(cnt==9)

cnt<=0;

else

cnt<= cnt+1;

end

always@(posedge clk)

begin

if(!rst)

plus<=0;

else if(cnt==9)

plus<=1;

else

plus <=0;

end

endmodule

仿真代码:

`timescale 1ns / 1ps

module cnt_tb( );

reg clk;

reg rst;

wire[7:0] cnt;

wire plus;

cnt cnt_init(.clk(clk),.rst(rst),.cnt(cnt),.plus(plus));

initial

begin

clk <=0;

rst <= 0;

#20

rst <=1;

end

always #5 clk =~clk;

endmodule

仿真结果:

FPGA入门练习

FPGA入门练习