一段状态机示例

2025-03-02

27

0

`timescale 1ns / 1psmodule mystate(input clk,input rst,output [2:0] out);reg[2:0] state;always@(posedge clk)beginif(!rst)state <= 2'b00;else if(state == 2'b00)state <= 2'b01;else if(state == 2'b01)state <= 2'b10;else if(state == 2'b10)state <= 2'b11;elsestate <= 2'b00;endassign out = state;endmodule

测试示例:

`timescale 1ns / 1psmodule Hellotmystate();wire[2:0] myout;reg rst;reg clk;mystate myinstance(.clk(clk),.rst(rst),.out(myout));initial beginrst = 0;clk = 0;#10rst = 1;endalways #5 clk =~clk;endmodule

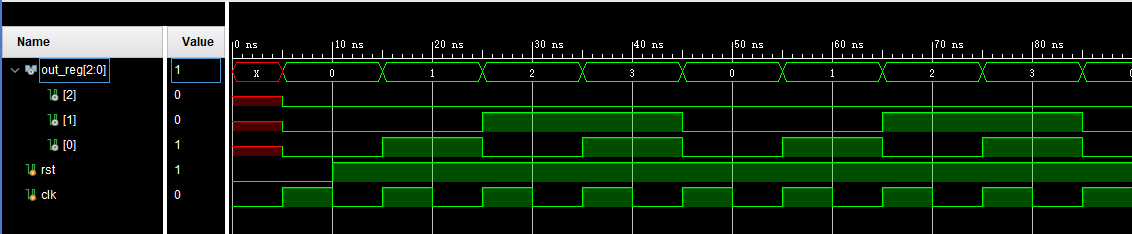

仿真结果:

输出为reg类型:

module mystate(input clk,input rst,output reg[10:0] count );always@(posedge clk)beginif(!rst)count<=10'b0;elsecount<= count+3;endendmodule

FPGA入门练习

FPGA入门练习