38译码器

2024-04-30

58

0

源代码:

`timescale 1ns / 1ps

module decode(a,b,c,out);

input a;

input b;

input c;

output reg[7:0] out;

always@(*)

begin

case ({c,b,a})

3'b000:out<=8'b00000001;

3'b001:out<=8'b00000010;

3'b010:out<=8'b00000100;

3'b011:out<=8'b00001000;

3'b100:out<=8'b00010000;

3'b101:out<=8'b00100000;

3'b110:out<=8'b01000000;

3'b111:out<=8'b10000000;

endcase

end

endmodule

仿真代码:

`timescale 1ns / 1ps

module decode_tb();

reg a;

reg b;

reg c;

wire[7:0] out;

decode decode_inst(

.a(a),

.b(b),

.c(c),

.out(out)

);

initial begin

a=0;

b=0;

c=0;

#20

a=1;

b=0;

c=0;

#20

a=0;

b=1;

c=0;

#20

a=1;

b=1;

c=0;

#20

a=0;

b=0;

c=1;

#20

a=1;

b=0;

c=1;

#20

a=0;

b=1;

c=1;

#20

a=1;

b=1;

c=1;

end

endmodule

`

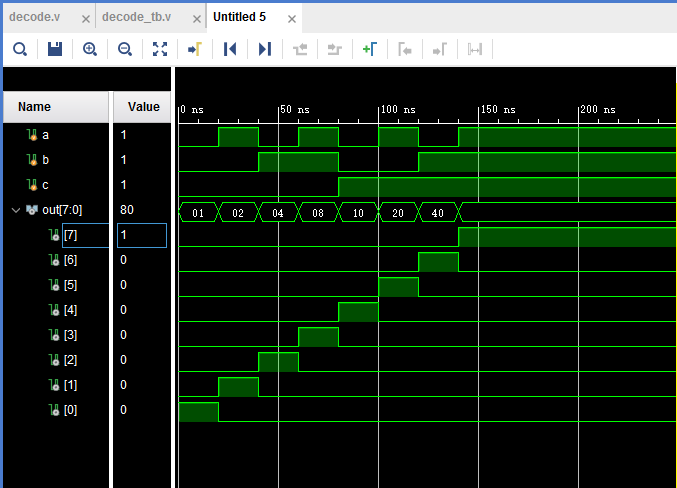

仿真结果如下:

FPGA入门练习

FPGA入门练习