PCIE6新要求、信令误差模型、错误处理及 Flit 模式

介绍

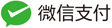

PCI Express ® (PCIe ® ) 架构已成为三十年来 I/O 连接的支柱,可实现组件之间的节能、高带宽和低延迟通信。作为其演进的一部分,PCI Express 技术刚刚以 64.0 GT/s 的速度推出了第六代,每代带宽都会翻倍,同时保持完全向后兼容性(图 1)。PCIe 技术在市场份额、容量和带宽方面继续领先于竞争的 I/O 技术,并且自其存在以来一直是整个计算连续体中无处不在的 I/O 互连。它的使用涵盖了手持设备、客户端、服务器、工作站、数据中心、高性能计算、汽车、嵌入式系统、工业应用等不同的细分市场。PCIe 技术凭借其引人注目的节能性能和成本效益而变得如此普遍,以至于其他协议(包括具有内存、存储和一致性语义的超延迟敏感的加载存储 I/O 协议(例如 Compute Express Link - CXL ®、NVM Express ®))可以在 PCIe PHY 上运行并利用 PCIe 基础设施(如上层、软件堆栈和平台连接)。

图 1:PCIe 规格历经三十年六代演进:带宽翻倍,具有领先的节能和成本效益性能,可满足整个计算连续体的需求,成为无处不在的互连

PCI-SIG®是一个由约 900 家成员公司组成的联盟,它拥有、管理和开发 PCIe 技术,并将其作为一项开放的行业标准。为了满足人工智能、机器学习、网络、通信系统、存储和高性能计算等新兴应用对带宽的无限需求,PCI-SIG 刚刚发布了第六代 PCIe 技术。本白皮书旨在深入了解 PCIe 6.0 规范所考虑的技术分析和权衡,以便以向后兼容的方式提供具有成本效益、可扩展和节能的性能。

PCIe 6.0 要求

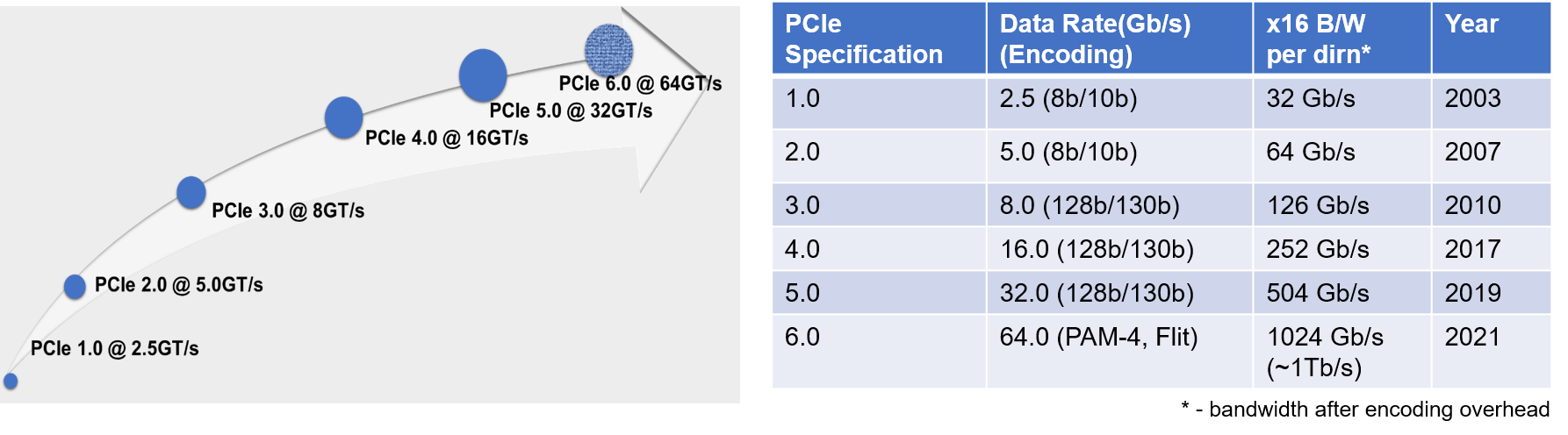

PCI Express 是一种加载-存储互连,具有极高的延迟、带宽和功率要求。部署 PCIe 技术的多个细分市场对可靠性和成本的要求也非常严格。作为无处不在的 I/O,PCIe 架构需要满足整个计算连续体中的这些要求,并具有完全的向后兼容性,如下表 1 所示。

表 1:PCIe 6.0 规范目标要求,满足部署 PCIe 技术的所有平台的需求

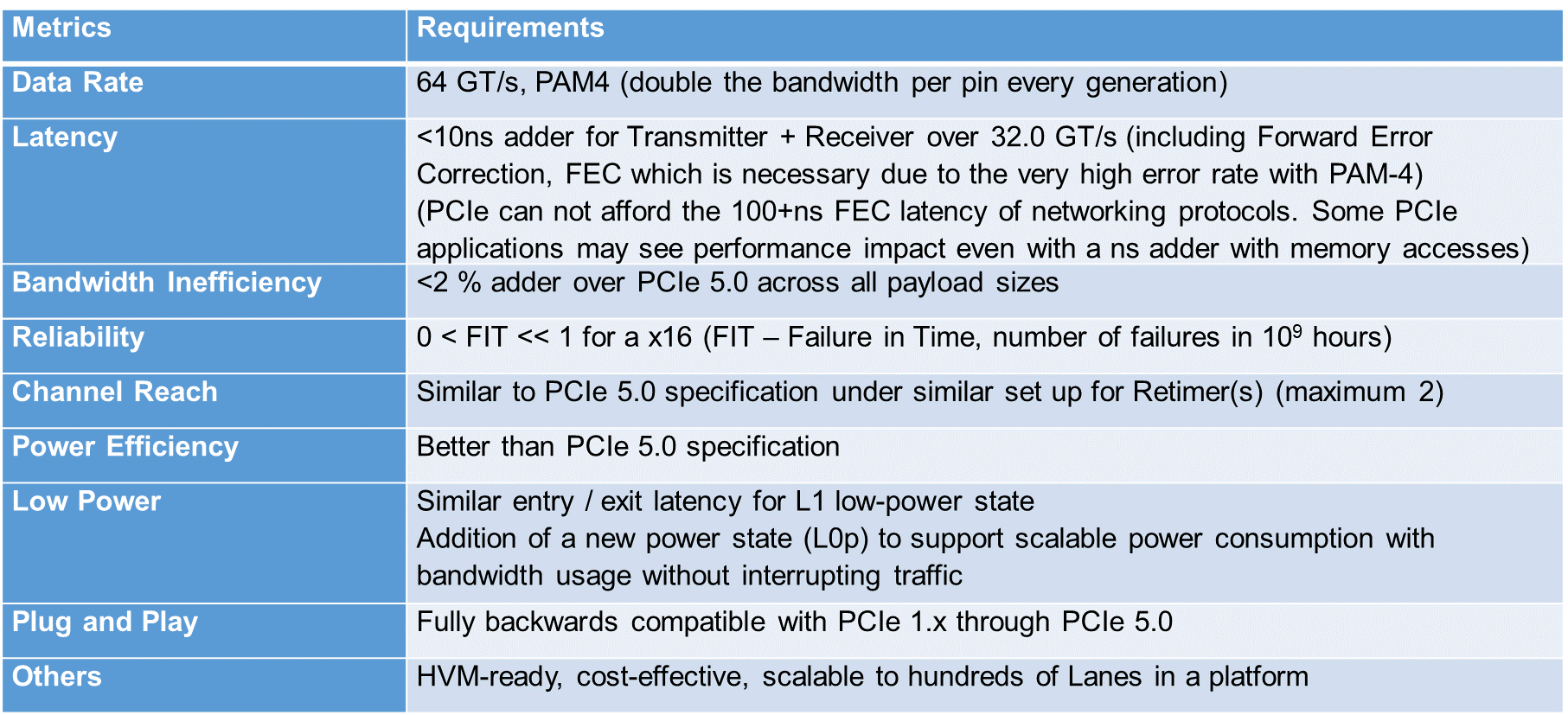

PAM4 信令的误差模型

PCIe 6.0 规范需要对封装、连接器和材料进行重大改进,就像我们在之前的速度提升中所做的那样。除了通道改进之外,PCIe 6.0 规范还使用 PAM4(脉冲幅度调制,4 级)信号来实现与 PCIe 5.0 规范类似的通道覆盖范围。PAM4 使用 4 个电压电平对 2 位数据进行编码,如图 2 所示,同时以与 PCIe 5.0 规范相同的 16G 奈奎斯特频率运行时钟。虽然 PAM4 有助于扩大通道覆盖范围,但它是以更高的误码率 (BER) 为代价的,在前五代 PCIe 规范中,误码率一直为 10 -12。BER是接收器中的误码数除以接收的总位数的度量。使用 PAM4 信号时,错误预计会成群出现,如图 2 所示。当发生位错误时,接收器中的决策反馈均衡器 (DFE) 可能会由于先前位错误的反馈传播而导致后续位中出现错误,从而导致突发错误。虽然可以通过适当选择 PHY 均衡方法、对 PAM4 的 4 级进行格雷编码和预编码等技术来减轻突发中的错误数量以及突发的长度,但需要解决通道中的突发错误。由于电源噪声等常见噪声源,链路中跨通道的其他形式相关性也是可能的。

图 2:由于 DFE 导致的通道内 PAM4 信令和突发错误,以及由于共同噪声源导致的通道间相关错误

采用 PCIe 6.0 架构以 64.0 GT/s 进行错误处理

使用 PAM4 编码,64.0 GT/s 的误码率 (BER) 预计会比过去五代 PCIe 规范中的 BER 10 -12差几个数量级。尽管 PCIe 架构具有链路级重试 (LLR) 机制来重放受错误影响的事务,但由于重试而导致的带宽损失使其无法承受 PAM4 错误率。因此,PCIe 6.0 规范使用轻量级 FEC 结合 LLR 机制来满足表 1 中列出的低延迟和低带宽开销的性能指标。

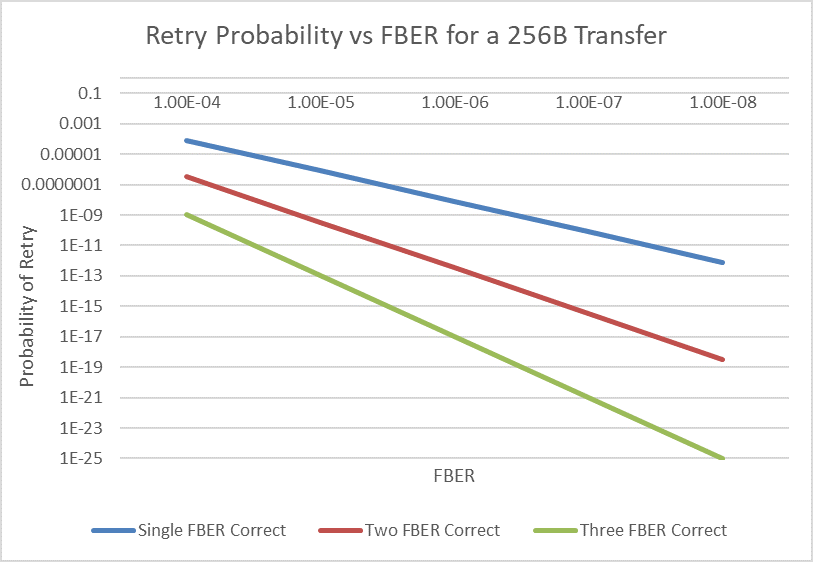

图 3:假设每个 FBER 实例都是一个可以通过 FEC 纠正的符号,则 x1 链路 256B 传输的重试概率与 FBER 的关系。这表明,单个 FBER 正确 FEC(FBER 为 10 -6)与低延迟重放机制相结合是满足 PCIe 应用严格延迟要求的最佳解决方案。即使是两个 FBER 正确 FEC 也会导致延迟增加数十纳秒。

PCIe 6.0 规范定义了一个称为“FBER”(第一位错误率)的参数。它是接收器引脚上发生(第一位)错误的可能性。如图 2b 所示,FBER 的发生可能会导致其他相关错误。从 FBER 计数的角度来看,所有这些单独的相关错误都算作一个错误。我们已经广泛研究了不同 FEC 功能下 FBER 与 FIT、重试概率和重试导致的带宽损失之间的权衡。图 3 显示了 x1 链路的简单研究作为说明。正如预期的那样,重试概率随着可以使用 256 字节有效载荷纠正的 FBER 实例数量而降低。但是,重试概率随着 FBER 的降低而呈指数下降。更强的 FEC 会导致更高的延迟,因为复杂性会随着纠正的符号数量呈指数增加。另一方面,较低的 FBER 会导致通道覆盖范围减小。我们选择了 3 路交错单符号校正 FEC(如图 4 所示)来校正 FBER 为 10 -6的单个 FBER 实例,以便在 10 -5范围内获得可接受的重试概率。这种轻量级使 FEC 校正延迟小于 2 纳秒。较低的 FBER 10 -6(与网络标准中的 10 -4相比)确实会导致通道覆盖范围缩短约 2-4 英寸。然而,尽管存在这种通道长度权衡,但我们仍在现有通道的通道覆盖范围内。此外,随着时间的推移,我们看到封装、材料和连接器不断改进,从而延长了通道覆盖范围,而更强的 FEC 对延迟的影响不会随时间而改变。因此,通过选择轻量级 FEC 和略微严格的 FBER,我们做出了正确的权衡,以保持延迟平稳,同时满足现有通道覆盖范围要求,并以严格的分析和硅数据为后盾。

我们的研究还表明,需要强大的 CRC 来实现非常低 FIT 的可靠性目标,因为要抵消相关性较高的错误率。我们选择 64 位 CRC 来保护每 256 个字节。我们的 CRC 基于 Reed-solomon 码,其中 g(x) = (x+α)(x+α 2 )… (x+α 8 ),其中 α 是 GF(2 8 )上本原多项式的根。这提供了一种非常强大的错误检测机制,因为它保证可以检测到最多 8 个字节的错误(FEC 后),并且在此之后的混叠概率为 2 -64。由于我们只检查综合征是否为零,因此 CRC 复杂度随位数的增加呈对数增加。因此,增加的 CRC 位数对门数或延迟的影响可以忽略不计。因此,轻量级 FEC 传送接收数据包时的错误概率约为 10 -5,而强 CRC 实际上可以保证检测到错误数据包(FIT 接近于 0,如表 2 所示),并且链路层重放将导致数据包在非常严格的低延迟约束内重新传输。

PCIe 6.0规范中的 Flit 模式

我们需要一个固定大小的传输实体(我们称之为 Flit,代表流量控制单元),以便可以应用 FEC 编码/解码/校正。有了固定的 Flit 大小,基于 CRC 的错误检测以及 ack/nak 和重试机制自然可以在 Flit 级别运行。

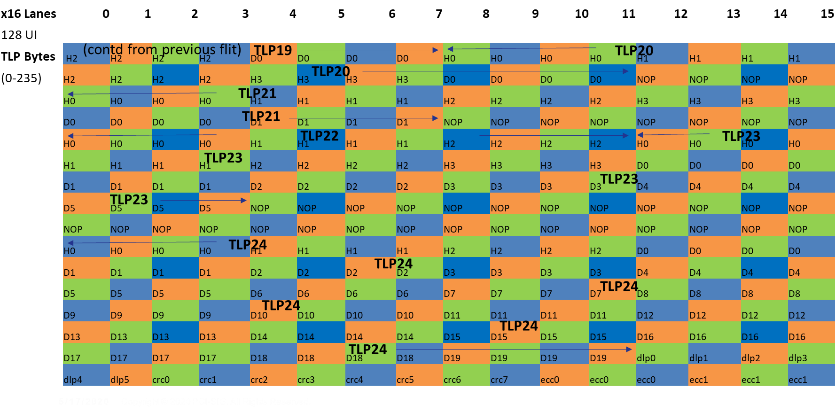

一个 Flit 可以有多个数据包(数据链路层数据包 - DLLP 和事务层数据包 - TLP),而一个 TLP/DLLP 可以跨越多个 Flits(如图 4 所示)。由于 Flit 包含 CRC,因此 DLLP 和 TLP 不会像前几代那样携带各自的 CRC 字节。由于 TLP/DLLP 在 Flit 中的位置固定,我们还删除了每个 TLP 或 DLLP 的 PHY 层帧令牌。固定的 DLLP 字节有助于可预测的低延迟重放机制并减少排队开销。这些机制有助于提高链路效率以克服 FEC 和 CRC 开销。

一个 Flit 包含 256 个字节。每个字节在一个 Lane 上发送,字节在链路的宽度上交错,与前几代的布局一致。Flit 的前 236 个字节用于 TLP,后面是 6 个字节用于数据链路层有效负载 (DLP),后面是 8 个字节用于 CRC,覆盖 TLP 和 DLP 的前 242 个字节,后面是 6 个字节的 FEC,覆盖整个 Flit。

图 4:x16 链路中 Flit 中的 TLP 排列

三个能够进行单符号纠正的 FEC 组在连续字节中交错,如图 4 中使用不同颜色组合所示。每种颜色代表不同的 FEC 组,分别由 85B、85B 和 84B 组成。由于这种三向 FEC 交错,只要突发长度 <= 16,就不会有突发错误影响同一 FEC 组的两个符号。因此,如果突发长度 <= 16 且通道间没有相关错误,则可以纠正 flit 中发生的一次 FBER。PCIe 6.0 规范通过限制 DFE(决策反馈均衡器)抽头权重并平衡发射机均衡 (TxEQ)、CTLE(连续时间线性均衡)和 DFE 均衡参数,确保突发长度 > 16 发生的概率小于 FBER。已经部署了其他技术(例如格雷编码和预编码)来减轻相关错误的影响。我们已经部署了广泛的分析来确保这一要求能够在部署 PCIe 技术的不同平台的广泛通道中得到满足。

性能和可靠性结果

我们在本节中介绍了各种指标。此处呈现的结果的详细数学分析可以在我们的 2021 IEEE Hot Interconnects 论文中找到。

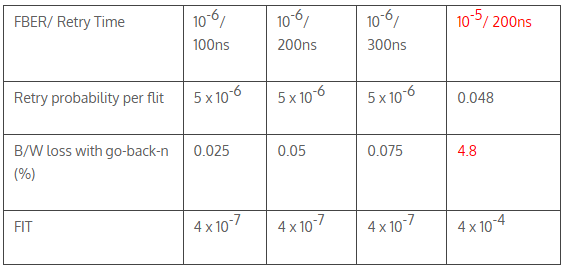

表 2 表明重试概率和带宽损失在预期之内。与前几代产品不同,Flit 重试在 64.0 GT/s 数据速率下很常见,尽管它们对带宽的影响很小。此外,由于预期重试时间约为 100 纳秒,我们预计不会看到太多抖动,因为它只是总访问时间的一小部分,并且在重试的情况下,加载系统中的排队延迟将远远超过额外的延迟。

表 2:基于 x16 链路的 FEC/CRC,重试概率、B/W 损失和 FIT 与 FBER 和重试时间的关系。10 -5 FBER列表明,带宽损失约为 5%,因此它不是一个可行的解决方案。重试在 PCIe 6.0 架构中很常见,但由于重试时间短,性能影响并不明显。

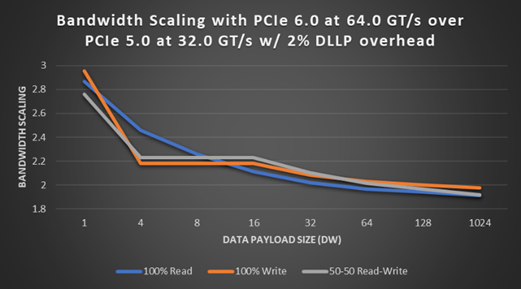

图 5 显示了 64.0 GT/s 的 Flit 模式与 32.0 GT/s 的 128b/130b 编码的带宽扩展。对于高达 512 字节(32 DW)的有效载荷,Flit 模式的数据包效率超过了 128b/130b 编码,从而使较小有效载荷的有效吞吐量提高了约 3 倍(数据速率提高了 2 倍,带宽效率提高了约 1.5 倍)。随着 TLP 大小的增加,这种效率会下降,对于 4KB 数据有效载荷大小,效率会降低到 0.98,与表 1 指标中提供的带宽效率低下一致。

图 5:Flit 模式的带宽扩展速度为 64.0 GT/s,而 128b/130b 编码的速度为 32.0 GT/s。对于实际系统,我们预计 PCIe 6.0 规范的可用带宽为 64.0 GT/s,而 PCIe 5.0 规范的可用带宽为 32.0 GT/s,前者为后者的 2 倍以上

Flit 模式下测量的延迟为 64.0 GT/s,低于前几代产品,但链路宽度较低(x1/x2)和有效载荷较小的 TLP(<= 16 B)除外。更高的数据速率可缩短数据包的传输时间。删除 Framing Token 和 Sync 报头等 PHY 编码机制可进一步降低延迟。例如,有效载荷为 256 B 的 TLP 的延迟减少量将超过 1ns。即使对于传输 3DW TLP 的 x1 链路,延迟增加量预计也将小于 10ns,满足表 1 的要求。

结论

我们已经证明 PCIe 6.0 规范满足或超出了表 1 中的所有要求。如果一项互连技术能够维持跨越十年的三代带宽改进,则该技术被认为是成功的。PCIe 架构已经远远超过了这一标准。随着我们进入第三个十年,PCIe 技术作为整个计算连续体中无处不在的 I/O 互连,前景看好。随着行业继续向第六代 PCIe 规范迈进,它将受益于它在高容量制造 (HVM) 环境中提供的节能性能,该环境具有数百条通道,可在一个平台上连接多个设备。

翻译原文:https://pcisig.com/blog/evolution-pci-express-specification-its-sixth-generation-third-decade-and-still-going-strong

pcie百科

pcie百科