PCIE基础概述

PCI Express(外围组件互连快速标准),正式缩写为PCIe或PCI-e,是一种高速串行 计算机 扩展总线标准,旨在取代旧的PCI、PCI-X和AGP总线标准。它是个人计算机的显卡、声卡、硬盘驱动器主机适配器、SSD、Wi-Fi和以太网硬件连接的通用主板接口。[2]与旧标准相比,PCIe 有许多改进,包括更高的最大系统总线吞吐量、更少的 I/O 引脚数和更小的物理占用空间、更好的总线设备性能扩展、更详细的错误检测和报告机制(高级错误报告,AER)和原生热插拔功能。PCIe 标准的较新修订版本为I/O 虚拟化提供了硬件支持。

PCI Express 电气接口以同时运行的通道数来衡量。(通道是一条发送/接收数据的单线,类似于一条双向各有一车道交通的“单车道公路”。)该接口还用于各种其他标准 - 最著名的是笔记本电脑扩展卡接口ExpressCard。它也用于SATA Express、U.2(SFF-8639)和M.2的存储接口。

格式规范由PCI-SIG(PCI特别兴趣小组)维护和开发,该小组由 900 多家公司组成,同时还维护传统的 PCI规范。

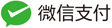

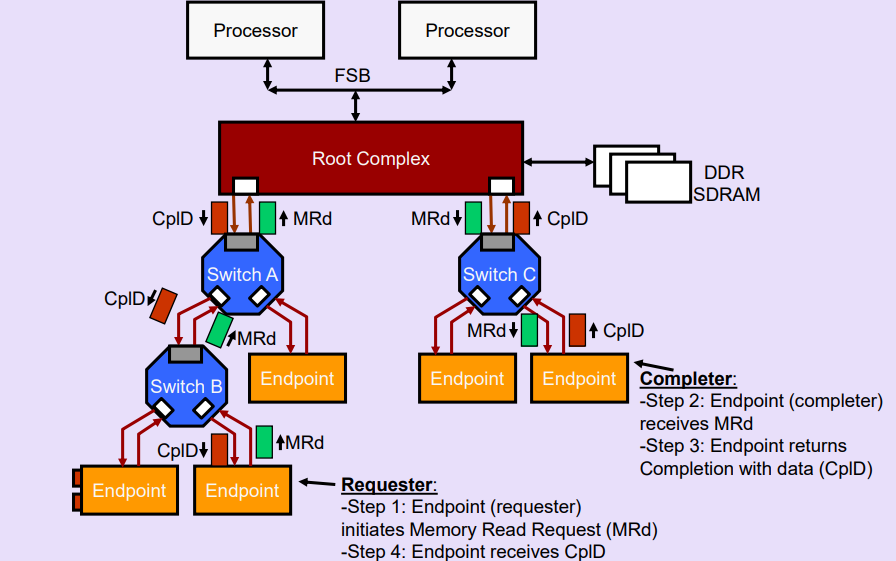

PCIE架构

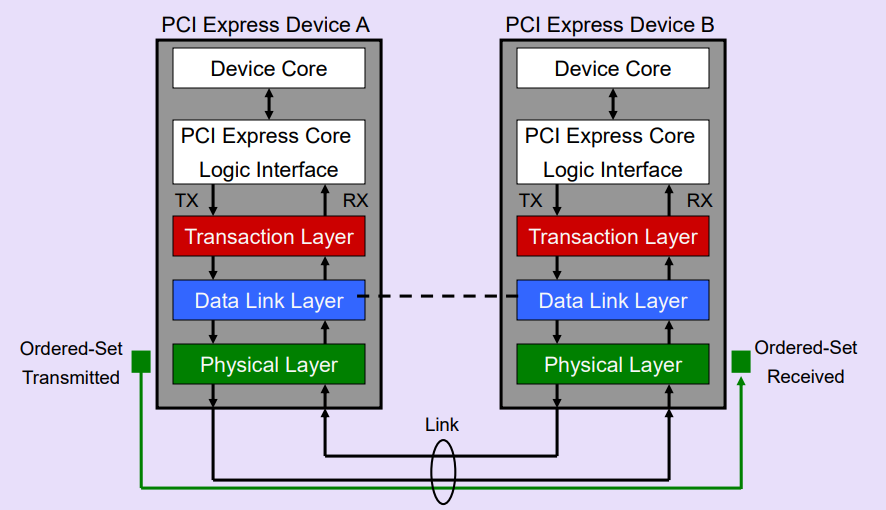

从概念上讲,PCI Express 总线是旧式 PCI/PCI-X 总线的高速串行替代品。PCI Express 总线和旧式 PCI 之间的一个主要区别是总线拓扑结构;PCI 使用共享并行总线 架构,其中 PCI 主机和所有设备共享一组公共的地址、数据和控制线。相比之下,PCI Express 基于点对点拓扑,具有将每个设备连接到根联合体(主机)的单独串行链路。由于其共享总线拓扑结构,对旧式 PCI 总线的访问是仲裁的(在多个主设备的情况下),并且在单个方向上一次只能访问一个主设备。此外,旧的 PCI 时钟方案将总线时钟限制为总线上最慢的外设(无论总线事务涉及哪些设备)。相比之下,PCI Express 总线链路支持任意两个端点之间的 全双工通信,并且对跨多个端点的并发访问没有固有限制。

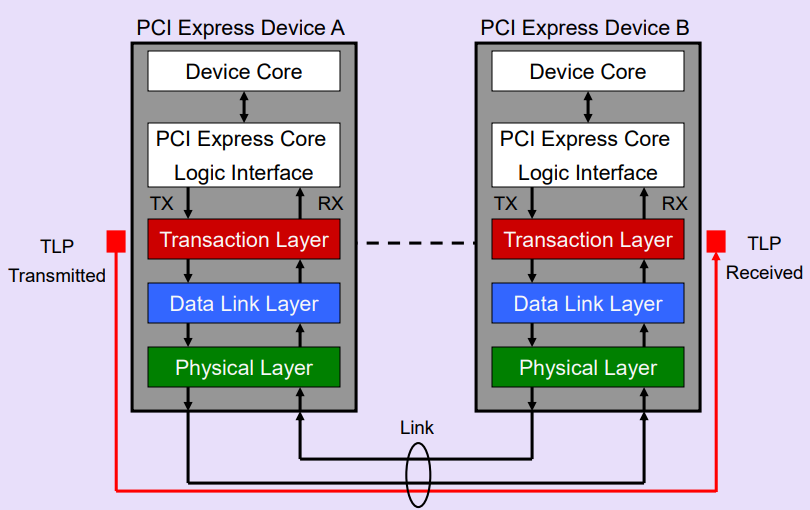

在总线协议方面,PCI Express 通信封装在数据包中。数据和状态消息流量的打包和解包工作由 PCI Express 端口的事务层处理(稍后介绍)。电气信号和总线协议的根本差异要求使用不同的机械外形尺寸和扩展连接器(因此需要新的主板和新的适配器板);PCI 插槽和 PCI Express 插槽不可互换。在软件级别,PCI Express 保留了与 PCI 的向后兼容性;旧式 PCI 系统软件可以检测和配置较新的 PCI Express 设备,而无需明确支持 PCI Express 标准,但新的 PCI Express 功能无法访问。

两个设备之间的 PCI Express 链路的大小可以从 1 个通道到 16 个通道不等。在多通道链路中,数据包数据被分到各个通道,峰值数据吞吐量与整个链路宽度成比例。通道数在设备初始化期间自动协商,并可由任一端点限制。例如,单通道 PCI Express (x1) 卡可以插入多通道插槽(x4、x8 等),初始化周期会自动协商最高的相互支持的通道数。链路可以动态地向下配置自身以使用更少的通道,从而在存在坏的或不可靠的通道时提供故障容忍度。PCI Express 标准定义了 x1、x2、x4、x8 和 x16 的链路宽度。直到 PCIe 5.0,x12 和 x32 链路也被定义但从未使用过。[8]这使得 PCI Express 总线既可以满足成本敏感型应用(不需要高吞吐量)的需求,也可以满足性能关键型应用(如 3D 图形、网络(10 千兆以太网或多端口千兆以太网)和企业存储(SAS或光纤通道)的需求。插槽和连接器仅针对这些宽度的子集进行定义,中间的链路宽度使用下一个更大的物理插槽大小。

作为参考,使用四通道 (x4) 的 PCI-X (133 MHz 64 位) 设备和 PCI Express 1.0 设备的峰值单向传输速率大致相同,均为 1064 MB/s。当多个设备同时传输数据或与 PCI Express 外设的通信是双向时,PCI Express 总线的性能可能优于 PCI-X总线。

PCIE通道

一个通道由两个差分信号对组成,一对用于接收数据,另一对用于发送数据。因此,每个通道由四条线或信号线组成。从概念上讲,每个通道都用作全双工 字节流,在链路的端点之间同时双向传输八位“字节”格式的数据包。[10]物理 PCI Express 链路可能包含 1、4、8 或 16 个通道。 : 4, 5 通道数以“x”为前缀(例如,“x8”代表八通道卡或插槽),其中 x16 是常用的最大尺寸。通道大小也通过术语“宽度”或“乘以”来表示,例如,八通道插槽可以称为“乘以 8”或“8 个通道宽”。

PCIE拓年结构

PCIE传输类型及地址空间

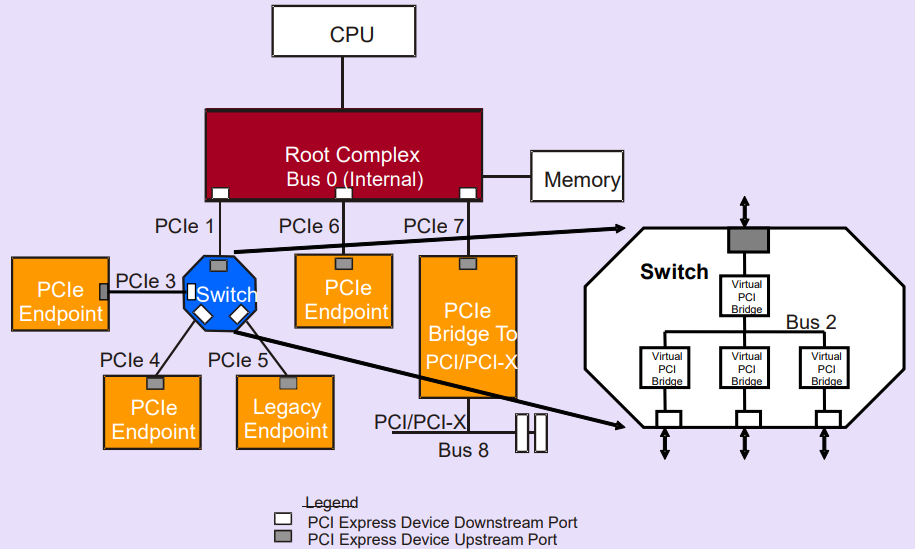

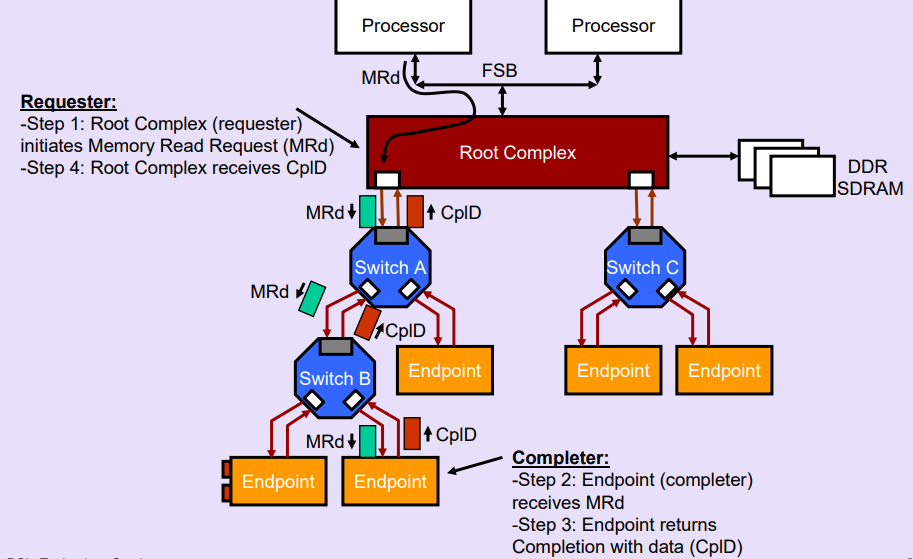

事务层将请求转换为四种事务类型之一:

1.内存读取或内存写入。用于从或向传输数据内存映射位置。

–该协议还支持锁定内存读取事务变体

2.I/O读取或I/O写入。用于在I/O位置之间传输数据。

–这些事务仅限于支持传统端点设备

3.配置读取或配置写入。用于发现设备

4KB PCI Express中的功能、程序特性和检查状态配置空间。

4.消息。处理方式与发布的内容一致。用于事件信号和通用消息传递

每个请求或完成标头都标记了其类型,每种数据包类型都基于三种方案之一进行路由:

- 地址路由

- ID路由

- 隐式路由

内存和IO请求使用地址路由

完成和配置周期使用ID路由

消息请求具有基于报头类型字段的消息路由子字段中的3位代码的可选路由

可编程IO事务

DMA传输

点对点传输

TLP源与目的地

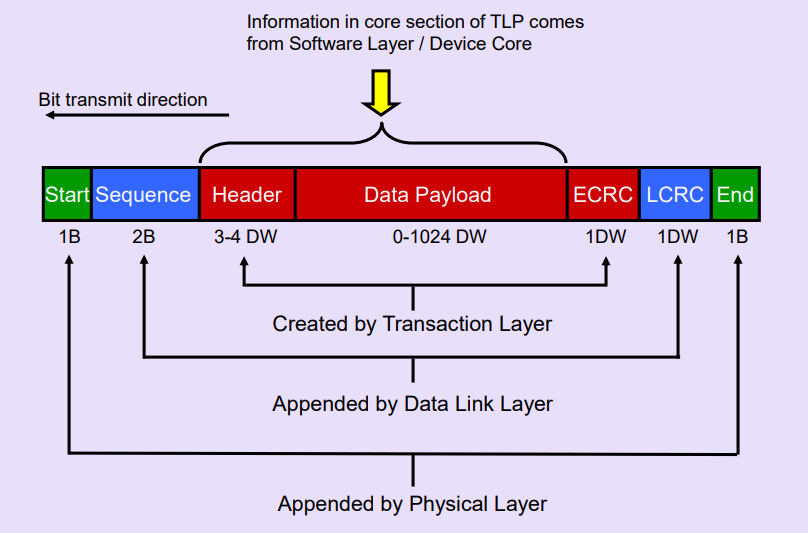

TLP结构

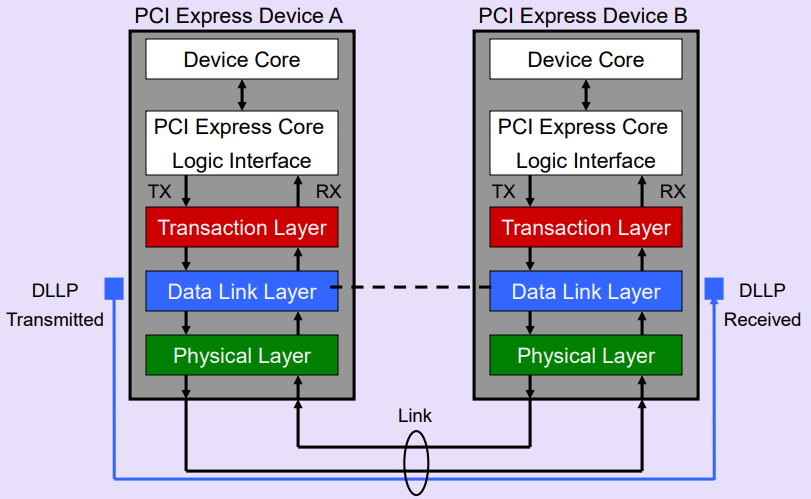

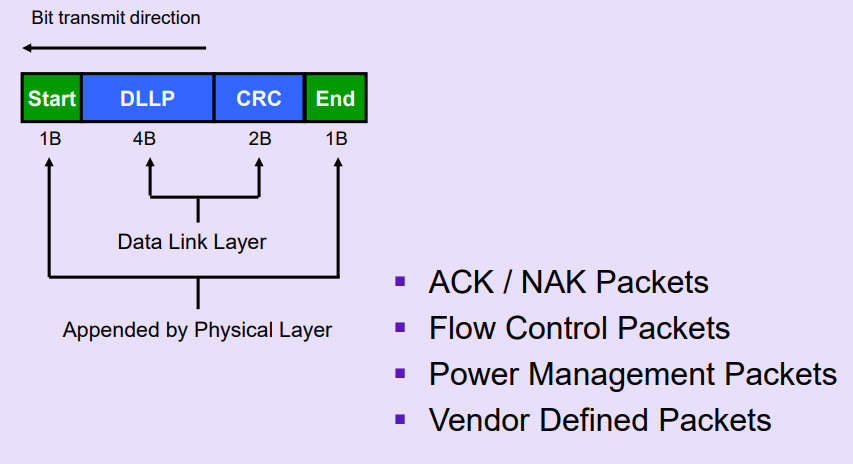

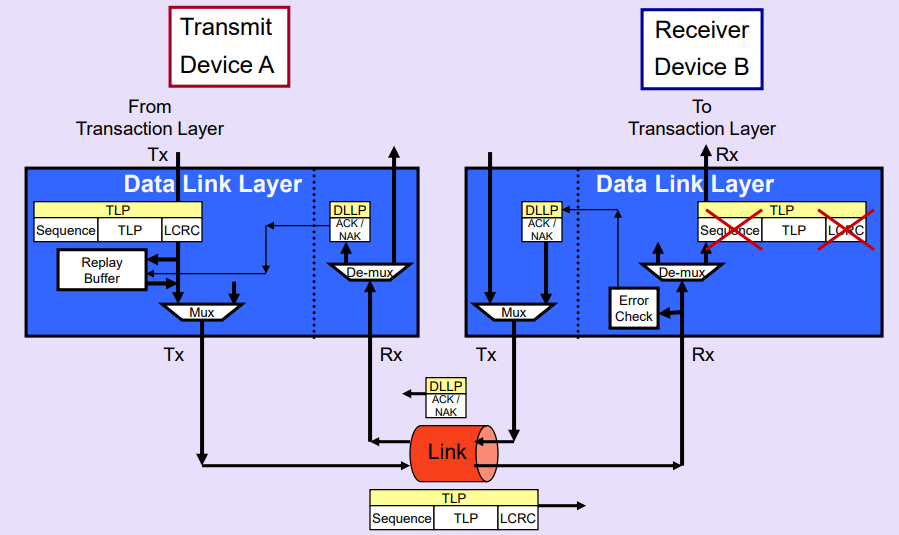

DLLP源与目的地

DLLP结构

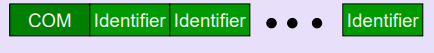

有序集合源与目的地

有序集合结构

Training Sequence One (TS1)

16 character set: 1 COM, 15 TS1 data characters

Training Sequence Two (TS2)

16 character set: 1 COM, 15 TS2 data characters

SKIP

4 character set: 1 COM followed by 3 SKP identifiers

Fast Training Sequence (FTS)

4 characters: 1 COM followed by 3 FTS identifiers

Electrical Idle (IDLE)

4 characters: 1 COM followed by 3 IDL identifiers

Electrical Idle Exit (EIEOS) (new to 2.0 spec)

16 characters

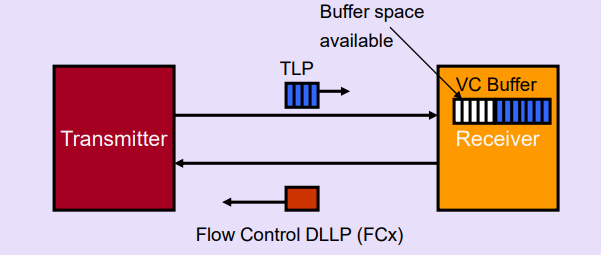

PCIE流控制

基于信用的流量控制是基于点对点的,而不是端到端的

接收器发送流控制包(FCP),这是一种DLLP(数据链路层包),为发射器提供信用,以便它可以向接收器发送数据包

ACK/NAK协议

文档参考:https://pcisig.com/sites/default/files/files/PCI_Express_Basics_Background.pdf

PCIE百科

PCIE百科